# FPGA based High Bandwidth LDPC using a Channel Coding Technique

M. Kasiselvanathan<sup>1\*</sup>, G. Sekar<sup>1</sup>, J. Prasad<sup>2</sup>, S. Lakshminarayanan<sup>1</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, Sri Ramakrishna Engineering College, Coimbatore, Tamil Nadu, India.

<sup>2</sup>Department of Electronics and Communication Engineering, KPR Institute of Engineering and Technology, Coimbatore, Tamil Nadu, India.

\*Corresponding author: kasiselvanathan@gmail.com

**Abstract:** Error-correcting codewords using Low-Density Parity Check (LDPC) have been the subject of many studies in the communications field. Because of their excellent error correction performance, low-complexity calculations, and appropriateness for parallel hardware design, they have also become typical digital modulation schemes in various protocols. Meanwhile, a lot of effort has gone into developing LDPC decoders that take advantage of the high processor speed and parallel processing of Field-Programmable Gate Array (FPGA) devices, which are now a viable alternative to Application-Specific Integrated Circuit (ASIC) systems for LDPC decoder implementations. However, the open literature FPGA-based LDPC encoder solutions differ widely in design choices and quality criteria, making them hard to compare and much more challenging to execute. A corrected signal decoding method with several design optimizations that lower the expenses of supporting several different codes. The decoder's development findings show that it can achieve better bandwidth utilization than earlier flexible FPGA-based LDPC decoders while still meeting the requisite amount of extensibility and satisfactory error-correcting effectiveness.

**Keywords:** AWGN, FPGA, ASIC, IFFT, LDPC, Encoder, Decoder.

## INTRODUCTION

Low-Density Parity-Check codes are a type of Forward Error Correction (FEC) code that may be used to repair transmission faults near the theoretical maximum in communication networks. They've had a resurgence since then, being the subject of a lot of study in the field of telecommunications and displaying the capacity for positive components based [1]. LDPC codes have indeed been incorporated in several current internet protocols, including IEEE 802.11n, because of the increased processing of electricity produced today. LDPC codes have a variety of desirable characteristics that make them suitable for the application. The LDPC decoding technique may be performed with reduced calculations, resulting in processor hardware with a cheap testing and construction cost [2]. The LDPC decompression algorithm's intrinsic parallelism easily transfers to dispersed parallel compute units for moderately modulation applications.

LDPC codes are also decoded repeatedly, similar to turbo codes, reaching error-correcting to perform successfully to the theoretical maximum when processing communications with long block lengths [3]. In opposition to precoding, LDPC decoders may be designed with an extensive range of alternative algorithms and levels of parallelization, giving designers some options to choose from to obtain the necessary qualities. While different processing elements are comparatively simple to construct, the architecture of a complete LDPC decoder is a complex interaction of some functional features, including having to process bandwidth, associated with lost, device resource needs, error checking capability, required to process energy efficiency, high bandwidth, and extensibility [4]. The structure, the LDPC code utilized, the method used, and the frequency of decoding rounds are all factors that influence these properties [5]. Designing an effective and efficient LDPC decoding is a problematic and time-consuming undertaking due to the intricate nature of the interactions between these factors and attributes.

A lesson on FPGA-based LDPC decoders is presented well before presenting our latest survey and innovative designs [6]. We do so by describing Forward Error Correction (FEC) in broad terms, introducing the concepts and abbreviations utilized throughout the rest of this work. The nature of the data supplied by the

Received: 16.01.2022 Revised: 01.03.2022 Accepted: 21.03.2022

Licensed under a CC-BY 4.0 license | Copyright (c) by the authors

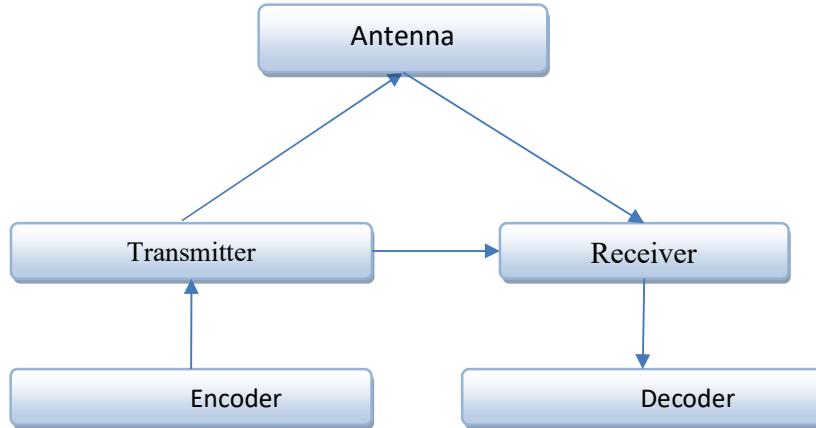

demodulator impacts the error-correcting capacity of an FEC decoder [7]. Figure 1 shows a transceiver channel of communication. Rather than employing serious choices to turn incoming symbols into packetized bits, an analog signal using soft preferences can provide better error detection and correction [8].

**FIGURE 1.** Transceiver Communication Channel

## PROPOSED METHOD

A decimation filter is beneficial at the receiver when an ADC samples the data at a greater frequency than the signal's frequency. Whenever the signal is amplified by the oscillation at the reception, undesired signals are produced. To reduce these unwanted signals, a lowpass filter is required. While the information may be retrieved from an oversampled signal, more calculations and hence more power is unnecessary [9]. The value of implementing more samples includes the ability to do better according to and estimates of the received symbol. Filter with many stages It is typically preferable to build the reduction filter in phases rather than in a single step [10]. The sample rate is reduced by a proportion of the total decrease at every stage. The constraints on the filters may be decreased by decreasing the sampling frequency in settings, leading to lower absorption of new duties [11].

Decoding an LDPC trigger word is significantly more complex than encoding since the decoder must examine every conceivable message word at the same time while functioning on the basis of hard decision LLRs rather than tricky communication bits [11]. As a result, we center our emphasis in this thesis on LDPC decoders. However, the encoding method is briefly detailed here for clarity. LDPC codes are commonly deciphered using a belief propagation (BP) technique in which information is repeatedly transferred down the edges between linked nodes in both directions [12]. Communications sent as inputs to a node are handled by energizing that node, which causes it to generate new output communications that are delivered back to the nodes to which it is linked. As a result, instead of having a single monolith global solution, the execution of the LDPC encoder is outsourced to the numerous distinctive computations conducted by the different nodes [13]. A vital feature of the fuzzy clustering method is that each message delivered to a specific node is independent of the message that was received after that node.

The LDPC decoder's schedule determines the Sequence in which nodes are activated [14]. The error-correcting capabilities of the LDPC decoder, including its other qualities The Sequence wherein VNs and CNs, are handled, including whether several sites are operated in parallel, are determined by the LDPC decoder process schedule[15]. There are many schedule variants. However, the three more prevalent are detailed, Layer Belief Propagation and Informed Dynamic Scheduling Flooding is maybe the most fundamentally straightforward LDPC decoding strategy. The component graph is handled iteratively in this case, with each iteration consisting of the input and output signal of all CNs, followed by the input and output signal of all VNs. LBP has the benefit that the knowledge gathered when in a repetition may be used to help the next iteration. Nevertheless, it lacks the same more fantastic standard of concurrency as the coding schedule, which may result in lower processor performance and increased processing delay. As contrasted to the usage has increased

timetable, it is seen that  $m$  CN activations and  $dc \times m$  VN activations occur every iteration, resulting in a more significant computational load per iterative process.

Carrier synchronization is required when the message can be impacted by phase and/or resonance frequencies and then when the synthesizers in the transmitter and person receiving the signal fluctuate in frequency. Carrier synchronization can be accomplished in two ways [16]. The first approach is to employ a prologue that the receiver may use to synchronize the frequency and loudness. The message signal is simply used to synchronize the carrier in the second step. Complete carrier synchronization and fine carrier synchronization are the two most common forms of carrier synchronization [17]. Because rough receiver synchronization occurs at periods, drifting clocks become such a concern when only coarse carrier synchronization is performed. Fine syncing can coordinate forever, but it can only synchronize slight differences. By executing a rough carrier synchronizing accompanied by acceptable carriers synchronizing, the significant error would be reduced to a proper error again for OK channel syncing [18]. Different architectures for different applications are discussed in [19-21].

To investigate how various algorithms evaluate one another, additional metrics other than power utilization must be assessed. In addition to power utilization, the transmission ratio will be estimated. The usage of eye sketches will be utilized to evaluate how well the instrumentation is performing.

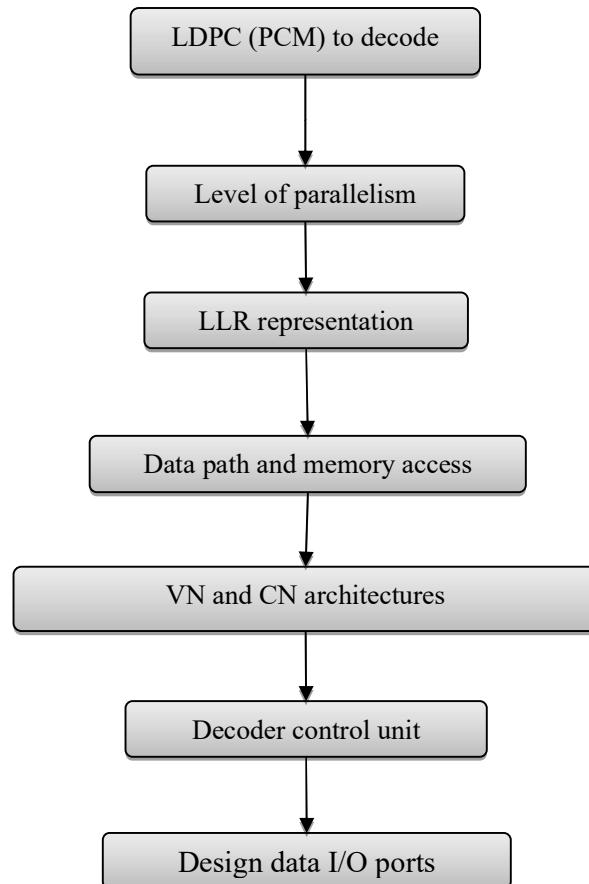

**FIGURE 2.** Proposed LPDC Decoder Stages

In addition to data processing facilities and memory, an LDPC decoder needs to incorporate hardware to regulate the entire iterative decoding process seen in Figure 2. This must offer an external command signal for initiating, terminating, and resetting the decoded operation but also selecting who of the permitted PCMs to utilize. The controller must also decide whether or not the decoding operation was successful. These elements

are discussed in succession in the following sections. The fixed-point FPGA-based LDPC decoder design has been shown to provide a very high level of run-time flexibility, which was highlighted as a deficiency in state of the art in FPGA-based LDPC decoders. This fixed-point structure may be used to handle any arbitrary collection of Quasi-Cyclic derived from any combination of various contemporary communications standards. However, the expense of doing so necessitates a more significant number of hardware resources than is required for that other non-flexible encoder and decoder in the academic research. This is due to the high amount of flexible routing required by flexible LDPC decoders to create complicated links in changing factor graphs. This issue is compounded by the use of inter-node Logarithmic-Likelihood Ratio (LLR) messages with multiple bits, which consume the majority of the FPGA's networking or logical resources. This high hardware utilization also results in long critical pathways through the decoder, which reduces the highest allowable frequency response and throughput.

## RESULTS AND DISCUSSIONS

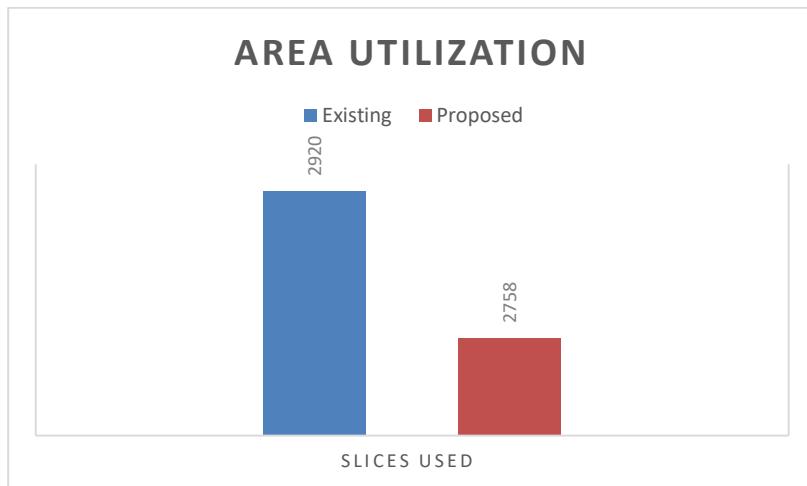

Attempting to lower the hardware requirements of a fixed-point decoder by reducing the width of the fixed-point LLRs, in particular, may have a significant negative influence on the decoder's error correction performance. It may be attributed to the lower quantity and quality conveyed by LLRs with smaller breadth, as well as the reality that they get saturation more readily at maximal or lowest values. This has the effect of raising the likelihood that a little transmitted fault can result in an inaccurate bit with perfect certainty, introducing further errors in any associated nodes. Table 1 displays the slices for various randomized channel models.

TABLE 1. Summary of Different Methods

|                      | Existing method | Proposed method |

|----------------------|-----------------|-----------------|

| <b>Max frequency</b> | 140.73MHz       | 214.4MHz        |

| <b>Slices</b>        | 2920            | 2758            |

The Forwards-Backwards method is used in the Manual transmission design. The Sequence of data architecture, on the other hand, portrays all two purposes as clearly specified calculations, with the goal of mimicking the basic structure of an FPGA. Although this architecture has a shorter roadmap length, it necessitates much more logic capabilities than design alternatives.

FIGURE 3. The Performance of both Deployments.

This is about 1% less than the system's overall area usage. As seen in Figure 3, the efficiency of both installations is similar. Lookups designs calculate each output separately, removing the need for the reverse process.

## CONCLUSIONS

The integrated design row added an element of automated design-time flexibility to the FPGA-based LDPC decoding topologies shown. This is made more accessible by presenting the suggested designs in a completely generic way, allowing them to be tailored to any arbitrary collection of QC PCMs purely computer algorithms. This entails processing the chosen set of QC PCMs in order to obtain the critical decoder addressable. When the clocking rate and byte cannot be reduced any further, it is helpful to contrast various ways. Details of the computational methodologies used to construct many of the more complicated components of the suggested designs were also presented. Such elements reflect the synthesized decoder parts that predominate the final reading execution features, which drive the specific optimizations detailed here. Multiple parametrizations of this technology were again synthesized and described, revealing its potential to handle any mixture of PCMs in numerous cutting-edge wireless networking standards. The results indicate that the proposed resolved structure maintains its more significant degree of concurrency without sacrificing error correction efficiency, and therefore it is likewise capable of attaining better processing throughputs than any previous FPGA-based LDPC decoder without walk flexibility. However, this comes at the price of a usually greater underlying hardware need, owing to the demand for a large number of very sophisticated adaptable routing elements to connect multi-bit signals between Variables Node Processing Elements and Checking Node Processing Elements.

## REFERENCES

- [1]. J. Wang, N. Juarez, E. Kohm, Y. Liu, J. Yuan, and H. Song, 2019, “Integration of SDR and UAS for malicious wifi hotspots detection,” In *2019 Integrated Communications, Navigation and Surveillance Conf. (ICNS)* pp. 1-8.

- [2]. L. Dai, Y. Fang, Z. Yang, P. Chen, and Y. Li, 2021, “Protograph LDPC-coded BICM-ID with irregular CSK mapping in visible light communication systems,” *IEEE Trans. on Vehicular Tech.*, **70**(10), pp.11033-11038.

- [3]. O. Hiari, and R. Mesleh, 2017, “A reconfigurable SDR transmitter platform architecture for space modulation MIMO techniques,” *IEEE Access*, **5**, pp.24214-24228.

- [4]. R. Ferreira, J. Gaspar, P. Sebastião, and N. Souto, 2020, “Effective GPS Jamming Techniques for UAVs using low-cost SDR platforms,” *Wireless Personal Communications*, **115**(4), pp.2705-2727.

- [5]. M. Milicevic, C. Feng, L. M. Zhang, and P. G. Gulak, 2018, “Quasi-cyclic multi-edge LDPC codes for long-distance quantum cryptography,” *NPJ Quantum Information*, **4**(1), pp.1-9.

- [6]. Y. Zhang, K. Peng, Z. Chen, and J. Song, 2019, “Construction of rate-compatible raptor-like quasi-cyclic LDPC code with edge classification for IDMA based random access,” *IEEE Access*, **7**, pp.30818-30830.

- [7]. M. Stark, L. Wang, G. Bauch, and R. D. Wesel, 2020, “Decoding rate-compatible 5G-LDPC codes with coarse quantization using the information bottleneck method,” *IEEE Open J. of the Communications Society*, **1**, pp.646-660.

- [8]. D. Chen, N. Zhang, R. Lu, X. Fang, K. Zhang, Z. Qin, and X. Shen, 2018, “An LDPC code-based physical layer message authentication scheme with perfect security,” *IEEE J. on Selected Areas in Communications*, **36**(4), pp.748-761.

- [9]. Y. L. Chen, and K. Xu, 2021, “The impact of RMB’s SDR inclusion on price discovery in onshore-offshore markets,” *J. of Banking & Finance*, **127**, p.106124.

- [10]. D. Zoni, A. Galimberti, and W. Fornaciari, 2020, “Efficient and scalable FPGA-oriented design of QC-LDPC bit-flipping decoders for post-quantum cryptography,” *IEEE Access*, **8**, pp.163419-163433.

- [11]. W. Jeong, J. Jung, Y. Wang, S. Wang, S. Yang, Q. Yan, Y. Yi, and S. K. Kim, 2020, “SDR receiver using commodity wifi via physical-layer signal reconstruction,” In *Proc. of the 26th Annual Int. Conf. on Mobile Computing and Networking* pp. 1-14.

- [12]. Q. Chen, S. Hong, and Y. Chen, 2019, “Design of linking matrix in JSCC scheme based on double protograph LDPC codes,” *IEEE Access*, **7**, pp.92176-92183.

- [13]. S. Kaushal, and S. Sharma, 2013, “A  $2 \times 2$  FPGA-based WARP was tested for colored image transmission in MIMO systems,” *Int. J. of Science and Modern Eng.*, **1**(6).

- [14]. N. Kirubanandasarathy, and K. K. M. Rajmohan, 2010, Study and Survey about Mixed Radix FFT Processor in MIMO OFDM, *Int. J. of MC Square Sci. Res.*, **2**, pp. 47-52.

- [15]. J. C. Gentile, 2021, *FPGA-Based Adaptive Digital Beamforming Using Machine Learning for MIMO Systems* (Doctoral dissertation, Johns Hopkins University).

- [16]. S Murugan, S. Mohan Kumar, and T.R.Ganesh Babu, 2020, “Image processing- based Lung Tumor-Detection and Classification using 3D Micro-Calcification of CT Images, “*Int. J. of MC Square Scientific Res.* **12(1)**, pp. 1-10.

- [17]. MM Ismail, M Subbiah and S Chelliah, 2018, “Design of pipelined radix-2, 4 and 8 based multipath delay commutator (MDC) FFT, *Indian J. of Public Health Res. and Development*, **9(3)**, pp. 765–768.

- [18]. V Jaiganesh and S. Murugan, 2005, “PC based heart rate monitor implemented in xilinx fpga and analysing the heart rate,”*Proc. of the Third IASTED Int. Conf. on Circuits, Signals, and Systems, CSS 2005*, pp. 319–323.

- [19]. D. S. Lenin, and H. Shekar, 2016, “Design of Low Power Novel Gate,” *Int. J. Adv. Sig. Img. Sci.* **2(1)**, pp. 19–23.

- [20]. R. Nusullapalli and N. Vaishnavi, 2018, “Design of FFT Architecture Using Kogge Stone Adder,” *Int. J. Adv. Sig. Img. Sci.* **4(2)**, pp. 8–15.

- [21]. V. Ellapan and J. S. Alaric, 2019, “A Parallel and Pipelined Architecture for Cordic Algorithm,” *Int. J. Adv. Sig. Img. Sci.* **5(2)**, pp. 23–31.